Most of the slides in this lecture are either from or adapted from slides provided by the authors of the textbook "Computer Systems: A Programmer's Perspective," 2<sup>nd</sup> Edition and are provided from the website of Carnegie-Mellon University, course 15-213, taught by Randy Bryant and David O'Hallaron in Fall 2010. These slides are indicated "Supplied by CMU" in the notes section of the slides.

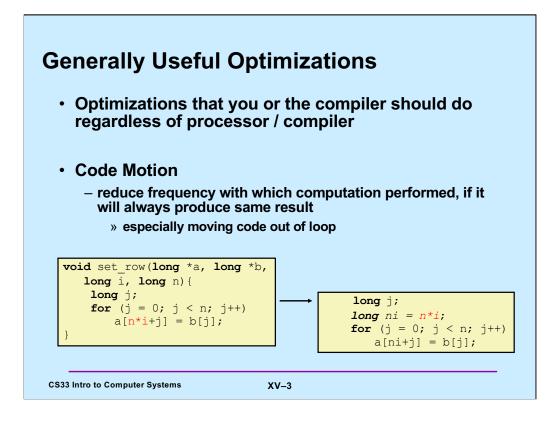

In this example, we think of a as being a pointer to a matrix and we're copying array b into one row of a.

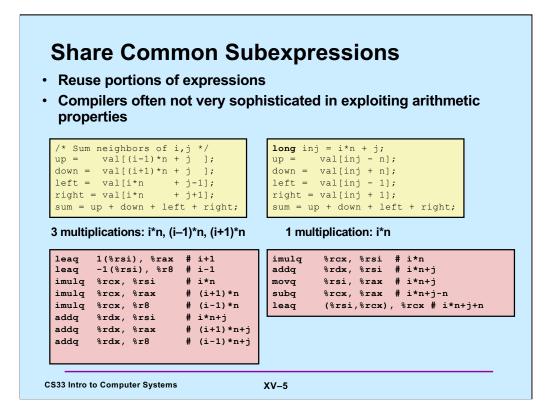

gcc does optimizations of the sort shown here.

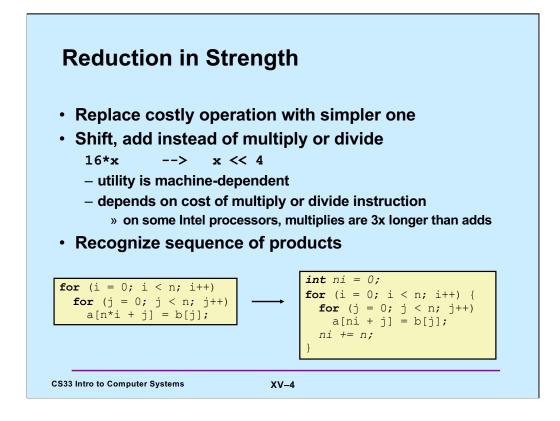

gcc doesn't always figure out the best way to compile code. The code in the lower-left box is what gcc produced for the code in the upper left box. On the right is a much better version that was done by hand. (The C code was modified by hand; gcc then produced the better assembly code.)

| Quiz 1                                                                                                     |         |                                                           |

|------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------|

| The fastest means for<br>n*n + 2*n + 1                                                                     | r evalı | uating                                                    |

| requires exactly:<br>a) 2 multiplies and<br>b) three additions<br>c) one multiply an<br>d) one multiply an | d two   | additions                                                 |

|                                                                                                            | Hir     | t: remember high-school algebra                           |

| CS33 Intro to Computer Systems                                                                             | XV–6    | Copyright © 2023 Thomas W. Doeppner. All rights reserved. |

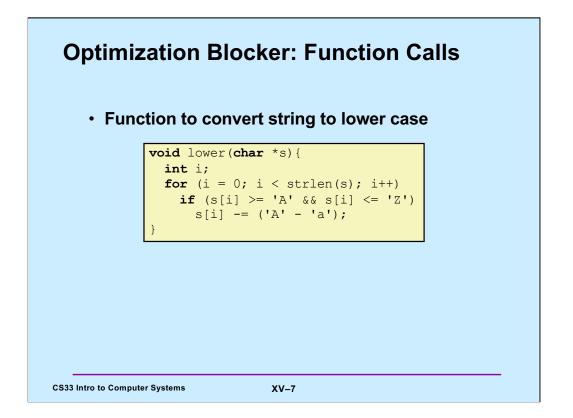

Note that the expression ('A' - 'a') is a constant and is probably computed by the compiler itself.

## **Improving Performance**

```

void lower2(char *s){

int i;

int len = strlen(s);

for (i = 0; i < len; i++)

if (s[i] >= 'A' && s[i] <= 'Z')

s[i] -= ('A' - 'a');</pre>

```

XV-11

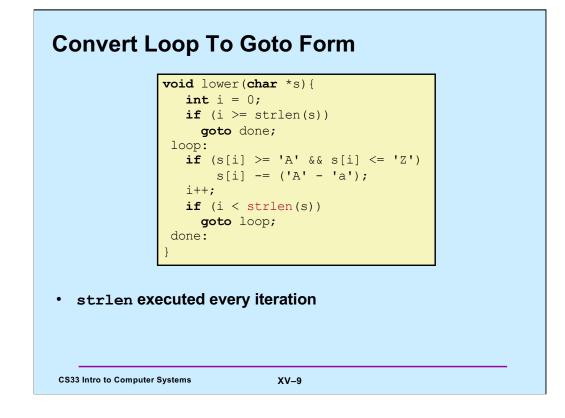

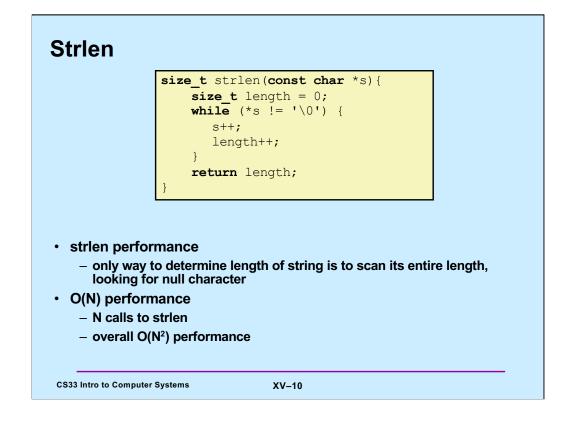

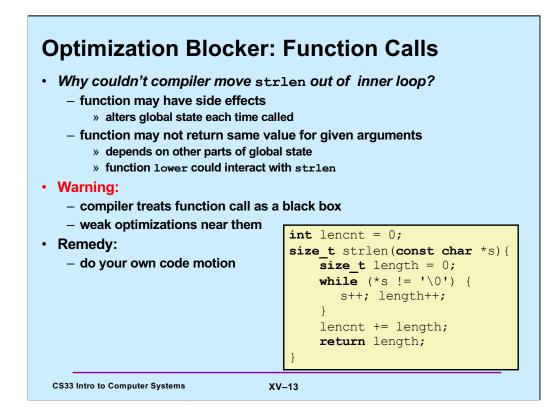

## • Move call to strlen outside of loop

- since result does not change from one iteration to another

- form of code motion

CS33 Intro to Computer Systems

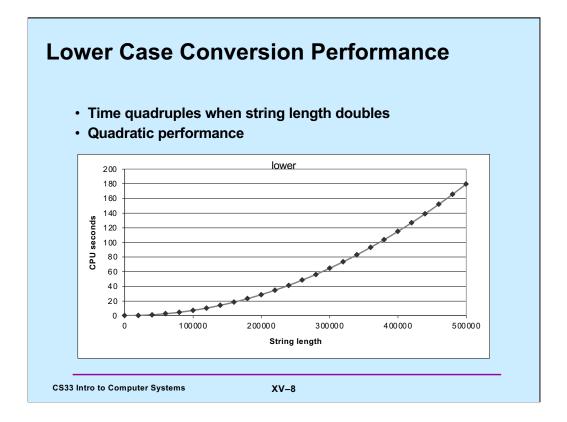

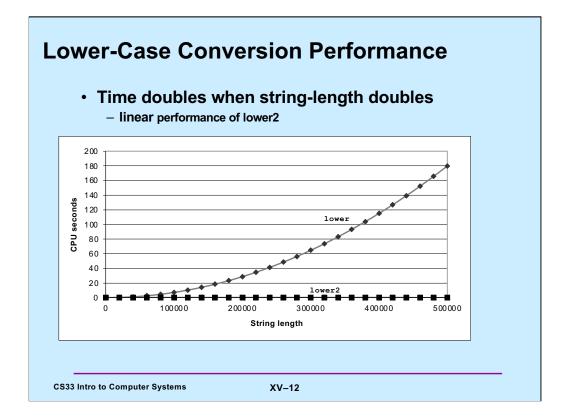

The plot of lower2's performance looks flat (constant time), but it's actually linear – the slope is too small to appear non-zero in this plot.

Based on a slide supplied by CMU.

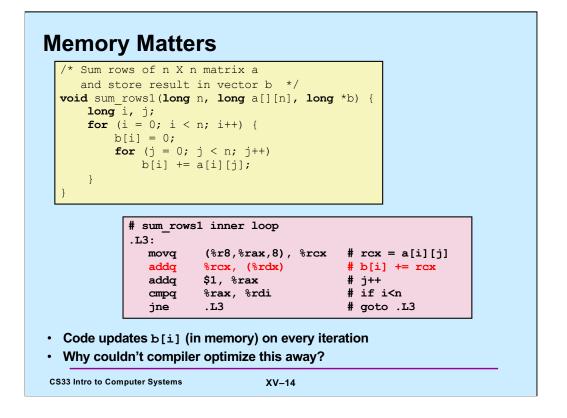

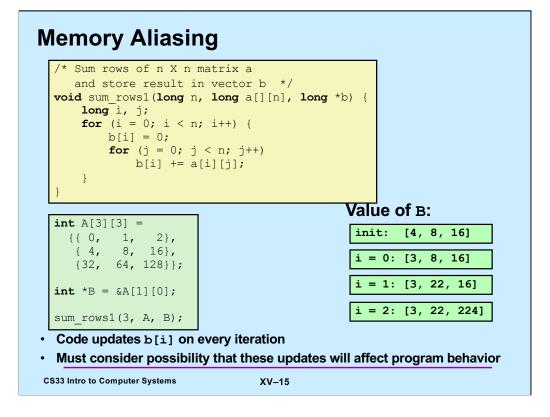

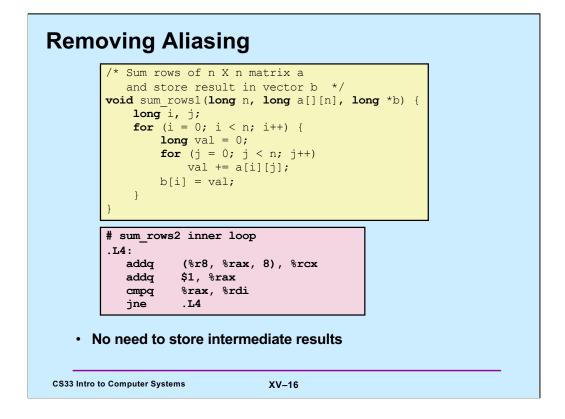

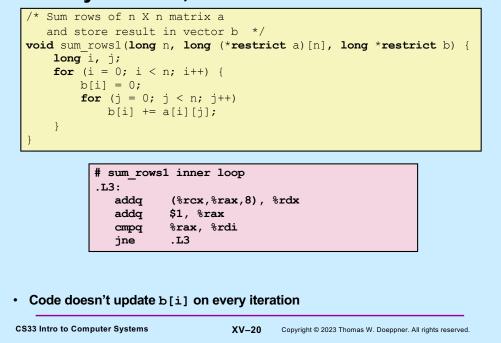

The issue here is whether it's really necessary to update the memory holding b[i] on every iteration of the inner for loop. Couldn't the value of b[i] be put in a register, updated there, then written to memory after the loop completes? Keep in mind that storing to memory is much more time-intensive than storing to a register.

Supplied by CMU, updated for current gcc.

Note that the programmer is implicitly assuming that the locations pointed to by a and b don't overlap.

## **Memory Matters, Fixed**

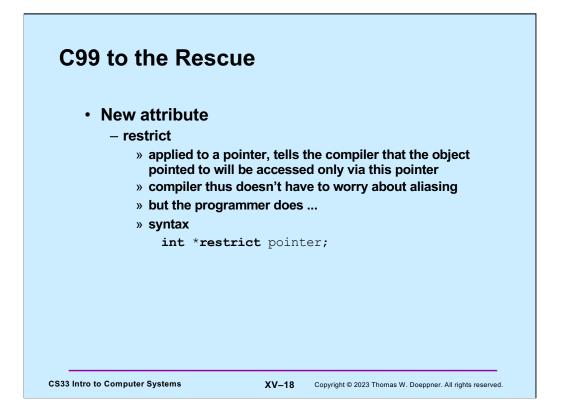

Note: we must give gcc the flag "-std=gnu99" for this to be compiled.

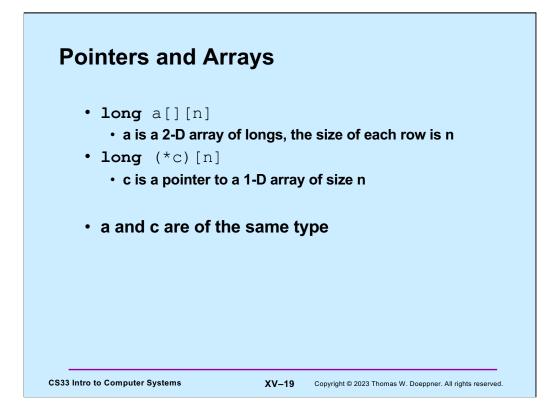

Observe that

**long** (\*a) [n]

declares a to be a pointer to an array of n longs.

Thus

```

long (*restrict a) [n]

```

declares a to be a restricted pointer to an array of n longs

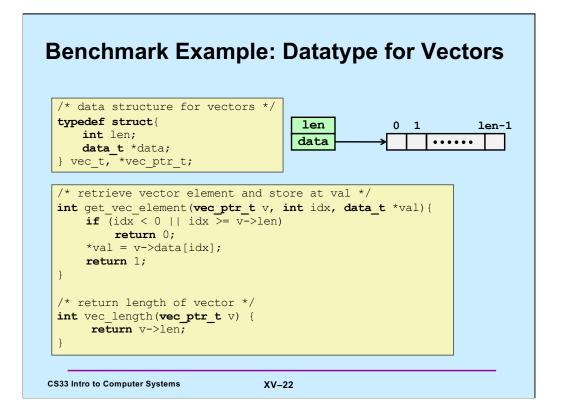

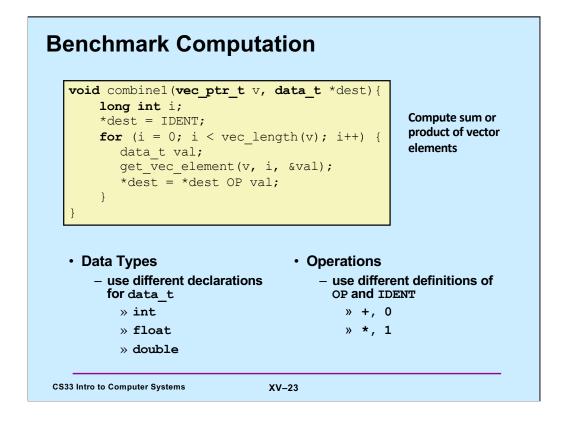

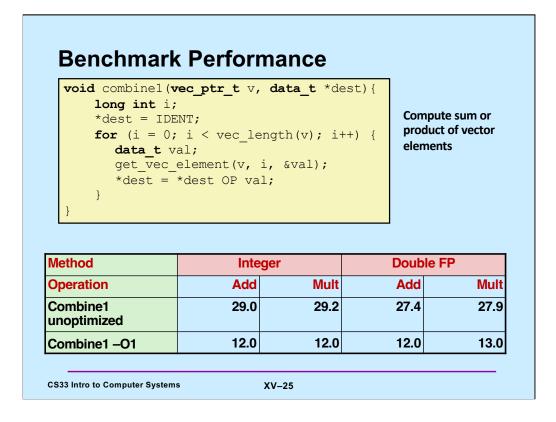

Note that **get\_vec\_element** not only does an array lookup, but also does bounds checking.

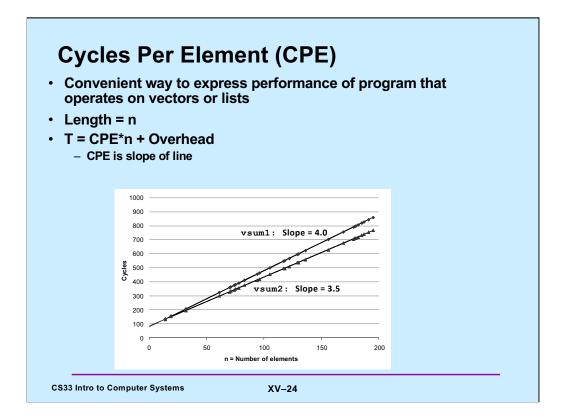

A **cycle** is a measure of processor time, often referred to as a **clock cycle**. Processors are driven by a clock, running at a certain frequency, say 10 GHz ( $10^{*}2^{30}$  cycles per second). In this case, the length of a cycle is the period of the clock (the reciprocal of its frequency -  $.1^{*}2^{-30}$  seconds).

The times given in the table are in cycles/element. The unoptimized code was compiled with the -O0 flag. The code would most likely be faster if compiled with the -O2 flag, but the purpose of these slides is to figure out exactly what can make it run faster.

| *dest = IDE<br>for (i = 0;<br>data_t v               | ength = vec_len<br>NT;<br>i < length; i<br>al;<br>element(v, i, | gth(v);      | st){ |              |

|------------------------------------------------------|-----------------------------------------------------------------|--------------|------|--------------|

|                                                      | *dest OP val;                                                   |              |      |              |

| *dest =                                              | *dest OP val;<br>Integer                                        |              | Dout | ole FP       |

| *dest =<br>}<br>}<br>Method                          |                                                                 | Mult         | Dout |              |

| *dest =<br>}<br>}<br>Aethod<br>Operation<br>Combine1 | Integer                                                         | Mult<br>29.2 |      | Mult         |

| *dest =<br>}<br>}                                    | Integer<br>Add                                                  |              | Add  | Mult<br>27.9 |

Since the result of calling **vec\_length** never changes, for the given vector v, there's no point to calling it in every iteration of the loop. So, we move it out of the loop and call it just once, with dramatic improvement of performance.

| <pre>long int i;<br/>long int length</pre>              | <pre>ptr_t v, data</pre>                    |      |        | <b>tr</b> v) {<br>v->data; |

|---------------------------------------------------------|---------------------------------------------|------|--------|----------------------------|

| <pre>for (i = 0; i &lt;     *dest = *des } Method</pre> | < length; i++)<br>st OP data[i];<br>Integer | {    | Double | FD                         |

| Operation                                               | Add                                         | Mult | Add    | , FF<br>Mult               |

| operation                                               | 8.03                                        | 8.09 | 10.09  | 12.08                      |

| Combine2                                                |                                             | 0.00 | 10.00  | 12.00                      |

Since bounds checking isn't necessary, we replace **get\_vec\_element** with a simple array lookup.

| int<br>int<br>data<br>data<br>for   | <pre>length = ve<br/>a_t *d = get<br/>a_t t = IDEN<br/>(i = 0; i &lt;<br/>= t OP d[i]</pre> | ec_leng<br>_vec_s<br>NT;<br>< lengt | th(v);<br>tart(v); | _ <b>_</b> |   |

|-------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------|--------------------|------------|---|

| *des<br>}                           | st = t;                                                                                     |                                     |                    |            | I |

| }                                   | Integer                                                                                     |                                     | Double             | FP         | J |

| }<br>Method                         |                                                                                             | Mult                                | Double<br>Add      | FP<br>Mult |   |

| Method<br>Operation<br>Combine1 –O1 | Integer                                                                                     | Mult<br>12.0                        |                    |            | I |

Finally, we recognize that we don't need to update **\*dest** on each iteration, but only when we're done.

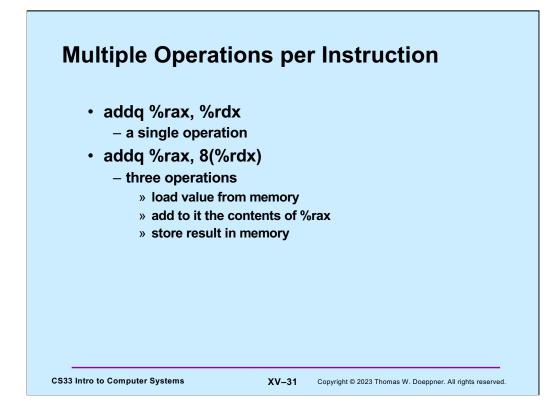

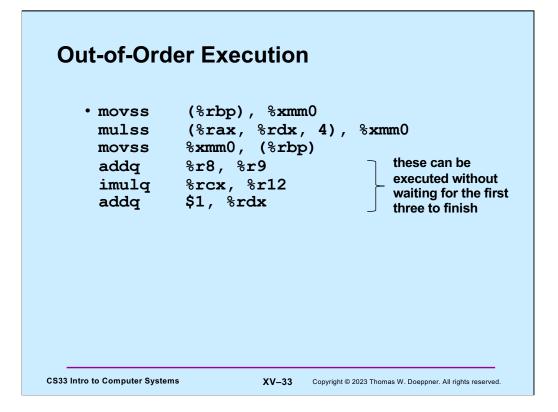

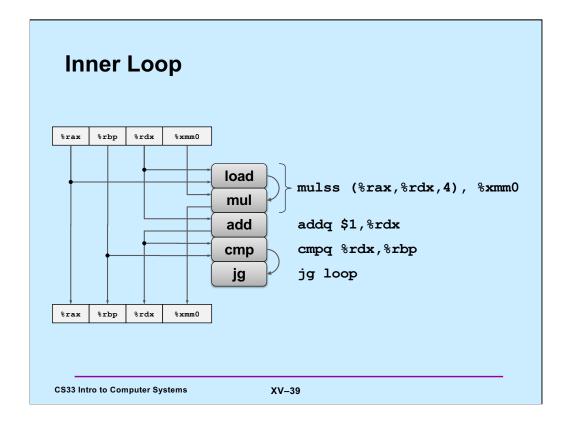

Note that the first three instructions are floating-point instructions, and %xmm0 is a floating-point register.

## **Speculative Execution**

| 80489f3: | movl  | \$0x1,%ecx         |                    |

|----------|-------|--------------------|--------------------|

| 80489f8: | xorq  | %rdx,%rdx          |                    |

| 80489fa: | cmpq  | %rsi,%rdx          |                    |

| 80489fc: | jnl   | 8048a25            |                    |

| 80489fe: | movl  | %esi,%edi          | perhaps execute    |

| 8048a00: | imull | (%rax,%rdx,4),%ecx | these instructions |

CS33 Intro to Computer Systems

XV-34 Copyright © 2023 Thomas W. Doeppner. All rights reserved.

| ng-point multiplication, integer and<br>rranches |

|--------------------------------------------------|

| ng-point addition, integer and floating-         |

| lion                                             |

| lion                                             |

|                                                  |

|                                                  |

| hes                                              |

| tion                                             |

|                                                  |

|                                                  |

|                                                  |

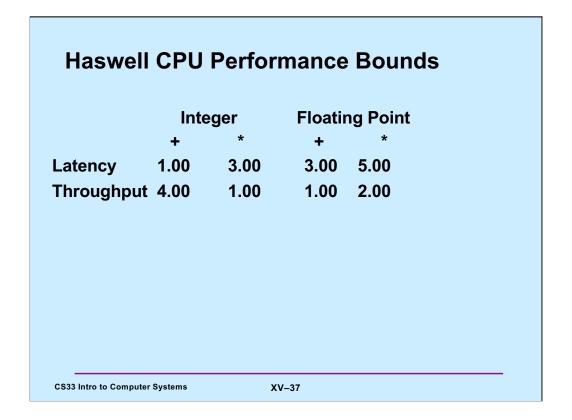

"Haswell" is Intel's code name for relatively recent versions of its Core I7 and Core I5 processor design. Most of the computers in Brown CS employ Core I5 processors.

While Apple's M1 and M2 processors have a different architecture, producing code for them involves similar concerns as producing code for Haswell processors.

| Instruction characteristics |         |              |          |  |  |

|-----------------------------|---------|--------------|----------|--|--|

| Instruction                 | Latency | Cycles/Issue | Capacity |  |  |

| Integer Add                 | 1       | 1            | 4        |  |  |

| Integer Multiply            | 3       | 1            | 1        |  |  |

| Integer/Long Divide         | 3-30    | 3-30         | 1        |  |  |

| Single/Double FP Add        | 3       | 1            | 1        |  |  |

| Single/Double FP Multiply   | 5       | 1            | 2        |  |  |

| Single/Double FP Divide     | 3-15    | 3-15         | 1        |  |  |

| Load                        | 4       | 1            | 2        |  |  |

| Store                       | -       | 1            | 2        |  |  |

|                             |         |              |          |  |  |

These figures are for those cases in which the operands are either in registers or are immediate. For the other cases, additional time is required to load operands from memory or store them to memory.

"Cycles/Issue" is the number of clock cycles that must occur from the start of execution of one instruction to the start of execution to the next. The reciprocal of this value is the throughput: the number of instructions (typically a fraction) that can be completed per cycle.

"Capacity" is the number of functional units that can do the indicated operations.

The figures for load and store assume the data is coming from/going to the data cache. Much more time is required if the source or destination is RAM.

The latency for stores is a bit complicated – we might discuss it in a later lecture.

Derived from a slide provided by CMU.

We assume that the source and destination are either immediate (source only) or registers. Thus, any bottlenecks due to memory access do not arise.

Each integer add requires one clock cycle of latency. It's also the case that, for each functional unit doing integer addition, the time required between add instructions is one clock cycle. However, since there are four such functional units, all four can be kept busy with integer add instructions and thus the aggregate throughput can be as good as one integer add instruction completing, on average, every .25 clock cycles, for a throughput of 4 instructions/cycle.

Each integer multiply requires three clock cycles. But since a new multiply instruction can be started every clock cycle (i.e., they can be pipelined), the aggregate throughput can be as good as one integer multiply completing every clock cycle.

Each floating point multiply requires five clock cycles, but they can be pipelined with one starting every clock cycle. Since there are two functional units that can perform floating point multiply, the aggregate throughput can be as good as one completing every .5 clock cycles, for a throughput of 2 instructions/cycle.

| <b>XUU-U</b> | 64 Compila                                                          | ation           | of Co                                  | mbine    | <b>4</b>         |

|--------------|---------------------------------------------------------------------|-----------------|----------------------------------------|----------|------------------|

| • Inner      | loop (case: \$                                                      | SP float        | ing-poi                                | nt multi | ply)             |

|              | .L519:<br>mullss (%rax<br>addq \$1, %rc<br>cmpq %rdx, %<br>jg .L519 | ,%rdx,4),<br>lx | ************************************** | Loop:    | i[i]<br>Length:i |

|              | L                                                                   |                 |                                        |          |                  |

|              | Method                                                              | Inte            | ger                                    | Doub     | le FP            |

|              | Method<br>Operation                                                 | Inte<br>Add     |                                        |          |                  |

|              |                                                                     |                 | Mult                                   | Add      | Mult             |

|              | Operation                                                           | Add             | Mult<br>3.00                           | Add      | Mult             |

These numbers are for the Haswell CPU. The row labelled "Combine4" gives the actual time, in clock cycles, taken by each execution of the loop. The row labelled "Latency bound" gives the time required for the arithmetic instruction (integer add or multiply, double-precision floating-point add or multiply) in each execution of the loop. The last row, "Throughput bound", gives the time required for the arithmetic instructions if they can be executed without delays by the multiple execution units – i.e., there are no data hazards (as explained in the previous lecture).

This is Figure 5.13 of Bryant and O'Hallaron. It shows the code for the single-precision floating-point version of our example.

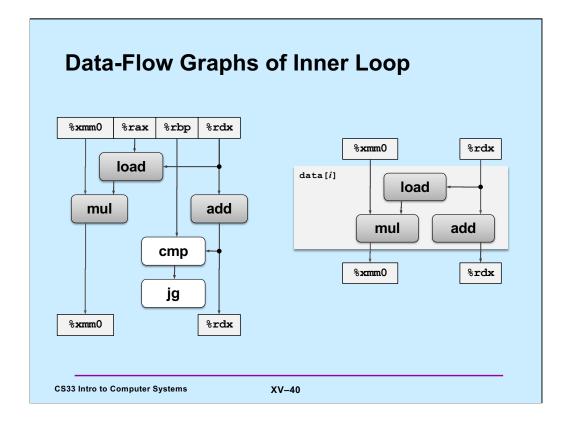

These are Figures 5.14 a and b of Bryant and O'Hallaron.

Since the values in %rax and %rbp don't change during the execution of the inner loop, they're not critical to the scheduling and timing of the instructions. Assuming the branch is taken, the **cmp** and **jg** instructions also aren't a factor in determining the timing of the instructions. We focus on what's shown in the righthand portion of the slide.

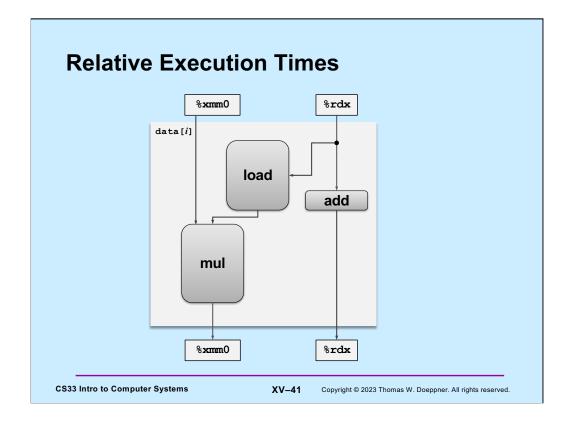

Here we modify the graph of the previous slide to show the relative times required of **mul**, **load**, and **add**.

This is Figure 5.15 of Bryant and O'Hallaron.

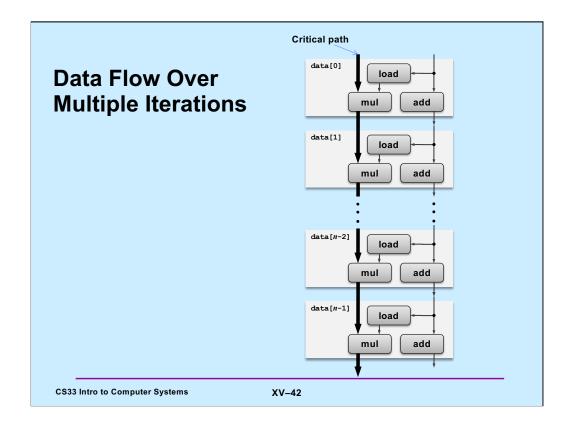

Without pipelining, the data flow would appear as shown in the slide.

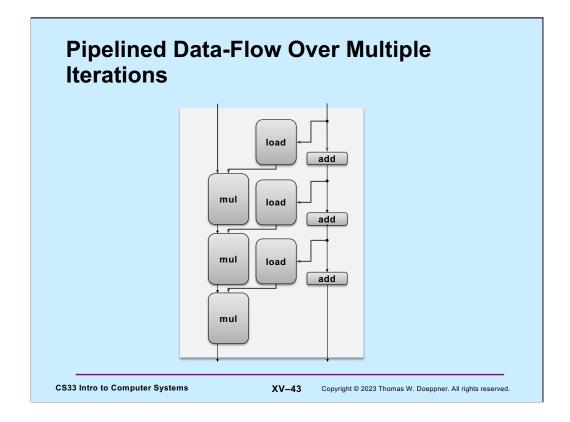

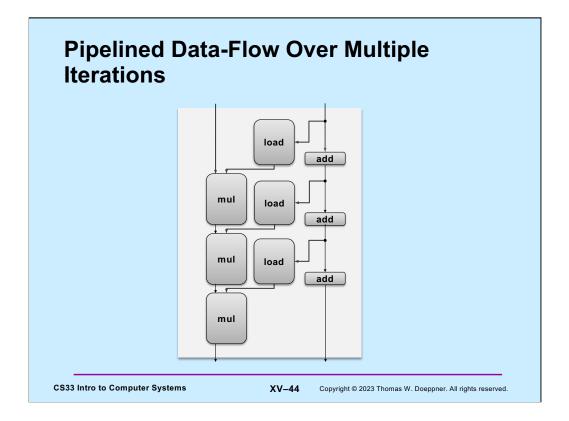

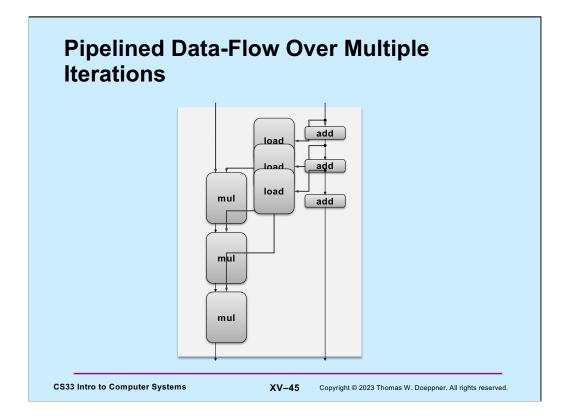

The loads depend only on the computation of the array index, which is quickly done by addition units. Thus, the loads can be pipelined.

It's clear that the multiplies form the critical path, since they use the results of the previous multiplies.

The loads depend only on the computation of the array index, which is quickly done by addition units. Thus, the loads can be pipelined.

It's clear that the multiplies form the critical path, since they use the results of the previous multiplies.

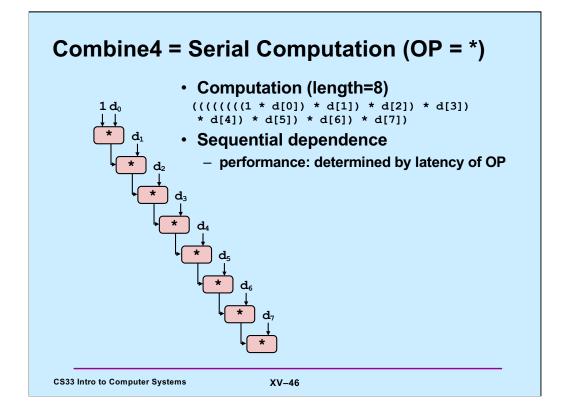

Since the multiplies form the critical path, here we focus only on them. In what's shown here, only one multiply can be done at a time, since the result of the one multiply is needed for the next.

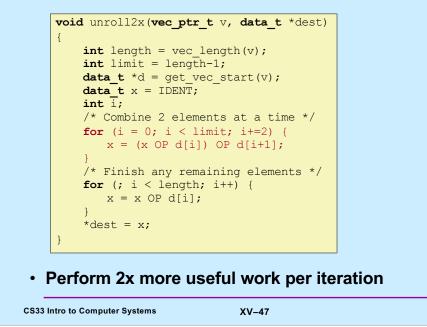

| Method                                               | Inte     | ger  | Double | e FP |

|------------------------------------------------------|----------|------|--------|------|

| Operation                                            | Add      | Mult | Add    | Mult |

| Combine4                                             | 1.27     | 3.00 | 3.00   | 5.00 |

| Unroll 2x                                            | 1.01     | 3.00 | 3.00   | 5.00 |

| Latency bound                                        | 1.0      | 3.0  | 3.0    | 5.0  |

| Throughput<br>bound                                  | 0.25     | 1.0  | 1.0    | 0.5  |

| os integer add<br>educes loop over<br>ers don't impr | rhead    | ıy?  |        |      |

|                                                      |          |      |        |      |

| till sequential de                                   | pendency | ,    |        |      |

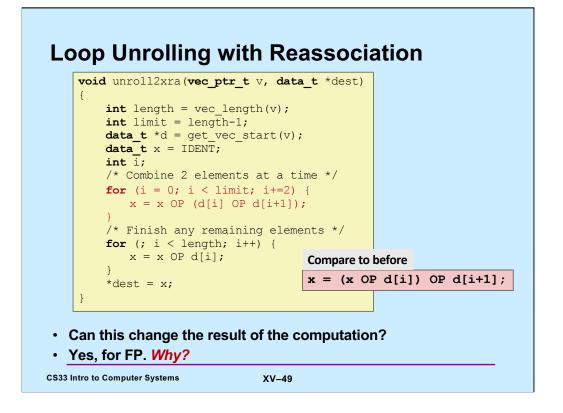

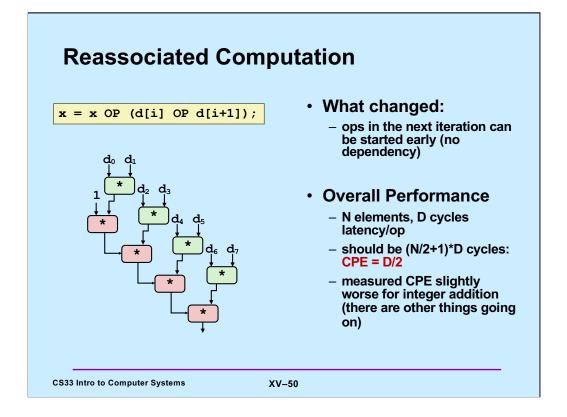

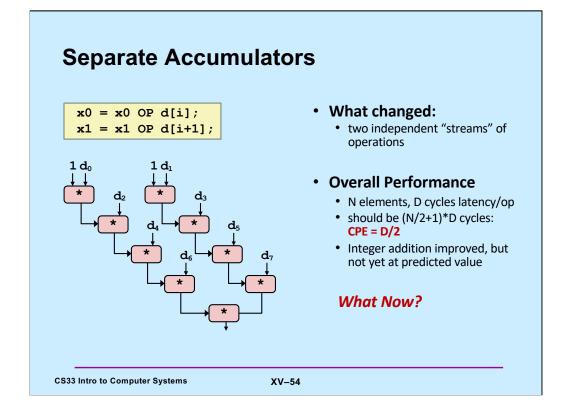

How much time is required to compute the products shown in the slide? The multiplications in the upper right of the tree, directly involving the  $d_i$ , could all be done at once, since there are no dependencies; thus, computing them can be done in D cycles, where D is the latency required for multiply. This assumes we have a sufficient number of functional units to do this, thus this is a lower bound. The multiplications in the lower left must be done sequentially, since each depends on the previous; thus, computing them requires (N/2)\*D cycles. Since first of the top right multiplies must be completed before the bottom left multiplies can start, the overall performance has a lower bound of (N/2 + 1)\*D.

| Method                                                              | Integer      |        | Double FP |      |

|---------------------------------------------------------------------|--------------|--------|-----------|------|

| Operation                                                           | Add          | Mult   | Add       | Mult |

| Combine4                                                            | 1.27         | 3.00   | 3.00      | 5.00 |

| Unroll 2x                                                           | 1.01         | 3.00   | 3.00      | 5.00 |

| Unroll 2x,<br>reassociate                                           | 1.01         | 1.51   | 1.51      | 2.51 |

| Latency bound                                                       | 1.0          | 3.0    | 3.0       | 5.0  |

| Throughput<br>bound                                                 | .25          | 1.0    | 1.0       | .5   |

| Nearly 2x speedup for<br>– reason: breaks seque<br>x = x OP (d[i] C | ential depen | ndency |           |      |

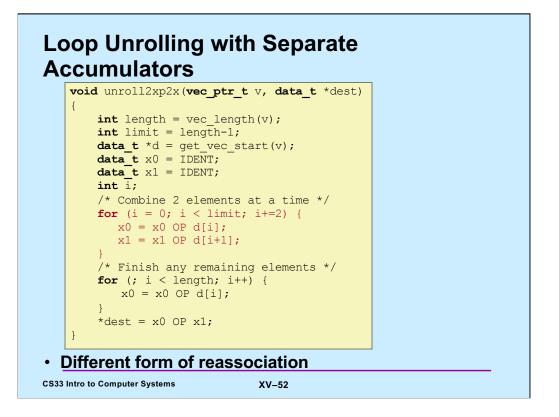

Here one "accumulator" (x0) is summing the array elements with even indices, the other (x1) is summing array elements with odd indices.

## **Effect of Separate Accumulators**

| Method                    | Inte | ger  | Doub | le FP |

|---------------------------|------|------|------|-------|

| Operation                 | Add  | Mult | Add  | Mult  |

| Combine4                  | 1.27 | 3.00 | 3.00 | 5.00  |

| Unroll 2x                 | 1.01 | 3.00 | 3.00 | 5.00  |

| Unroll 2x,<br>reassociate | 1.01 | 1.51 | 1.51 | 2.01  |

| Unroll 2x parallel 2x     | .81  | 1.51 | 1.51 | 2.51  |

| Latency bound             | 1.0  | 3.0  | 3.0  | 5.0   |

| Throughput bound          | .25  | 1.0  | 1.0  | .5    |

- breaks sequential dependency in a "cleaner," more obvious way

x0 = x0 OP d[i]; x1 = x1 OP d[i+1];

CS33 Intro to Computer Systems

XV-53

This is Figure 5.30 from the textbook.

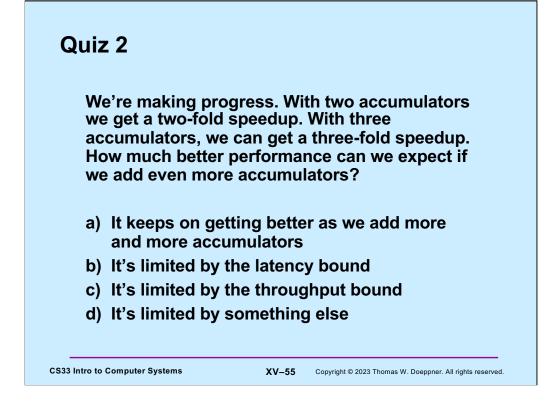

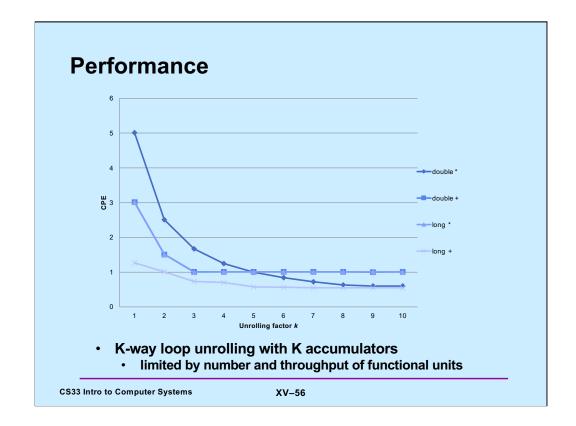

## Achievable Performance

| Method            | Inte | eger | Doub | le FP |

|-------------------|------|------|------|-------|

| Operation         | Add  | Mult | Add  | Mult  |

| Combine4          | 1.27 | 3.0  | 3.0  | 5.0   |

| Achievable scalar | .52  | 1.01 | 1.01 | .54   |

| Latency bound     | 1.00 | 3.00 | 3.00 | 5.00  |

| Throughput bound  | .25  | 1.00 | 1.00 | .5    |

CS33 Intro to Computer Systems

XV-57

Based on a slide supplied by CMU.

| lethod                             | Integer |      | Double FP |      |  |

|------------------------------------|---------|------|-----------|------|--|

| Operation                          | Add     | Mult | Add       | Mult |  |

| Combine4                           | 1.27    | 3.0  | 3.0       | 5.0  |  |

| Achievable Scalar                  | .52     | 1.01 | 1.01      | .54  |  |

| atency bound                       | 1.00    | 3.00 | 3.00      | 5.00 |  |

| Throughput bound                   | .25     | 1.00 | 1.00      | .5   |  |

| Achievable Vector                  | .05     | .24  | .25       | .16  |  |

| /ector throughput                  | .06     | .12  | .25       | .12  |  |

| Make use of S<br>– parallel operat |         |      | elements  |      |  |

|                                    |         |      |           |      |  |

Based on a slide supplied by CMU.

SSE stands for "streaming SIMD extensions". SIMD stands for "single instruction multiple data" – these are instructions that operate on vectors.

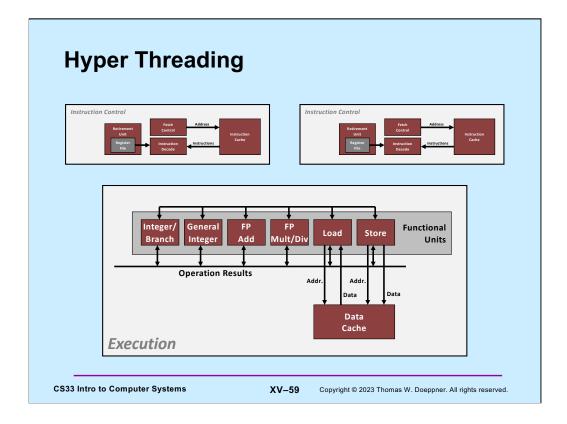

One way of improving the utilization of the functional units of a processor is hyperthreading. The processor supports multiple instruction streams ("hyper threads"), each with its own instruction control. But all the instruction streams share the one set of functional units.

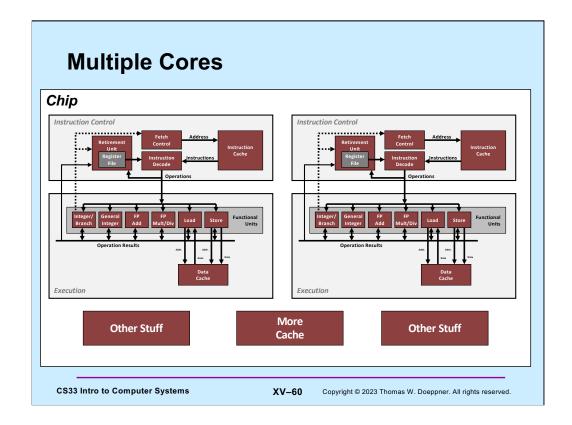

Going a step further, one can pack multiple complete processors onto one chip. Each processor is known as a core and can execute instructions independently of the other cores (each has its private set of functional units). In addition to each core having its own instruction and data cache, there are caches shared with the other cores on the chip. We discuss this in more detail in a subsequent lecture.

In many of today's processor chips, hyperthreading is combined with multiple cores. Thus, for example, a chip might have four cores each with four hyperthreads. Thus, the chip might handle 16 instruction streams.